随着科技的不断进步,芯片设计和制造技术也在持续发展。功耗的降低是近年来处理器发展的一个重要趋势,尤其是随着移动设备的普及,低功耗处理器的需求日益增加。CPU功耗的降低可以带来多方面的好处,包括延长电池续航时间、减少热量产生、降低冷却成本等。究竟是什么原因导致了CPU功耗降至3w这样低的水平呢?让我们深入探讨。

CPU功耗降低的技术驱动因素

在探讨降低CPU功耗的各种可能原因之前,首先需要了解CPU的基本工作原理。中央处理器(CPU)是计算机系统的核心部分,它通过执行复杂的指令集来处理数据。CPU的功耗与它的设计和制造工艺密切相关。以下是一些关键的技术因素,它们共同作用导致了CPU功耗的显著下降。

制造工艺的提升

随着半导体制造技术的演进,芯片的制程工艺越来越精细。从早期的微米级别到如今的纳米级别,晶体管的尺寸不断缩小,这使得在相同的面积内可以集成更多的晶体管。晶体管尺寸的缩小意味着在工作时所需电压的降低,从而直接减少了功耗。22纳米工艺相比90纳米工艺,可以显著降低工作电压和漏电流,进而减少功耗。

优化的微架构设计

除了硬件层面的制造工艺,CPU微架构的设计改进也是功耗降低的重要因素。通过优化处理器的内部设计,如增加执行单元并行度、改进指令调度和执行效率,以及使用更高级的预测算法来减少不必要的计算,可以使得CPU在完成相同工作量时消耗更少的能量。

动态电压频率调节

现代CPU通常都配备了动态电压频率调节(DVFS)技术,根据处理器负载动态调整电压和频率。当CPU负载较低时,处理器会降低工作频率和电压,从而大幅度减少功耗。这种技术让CPU在保持高性能的同时,在低负载时节省能量。

电源门控技术

电源门控技术是一种减少静态功耗的方法,静态功耗是由于晶体管即使在关闭状态下也会有微小的电流流动造成的。电源门控技术通过切断未活动晶体管的电源来减少这种功耗。这样,只有正在执行任务的部分晶体管处于工作状态,从而节约能源。

多核处理器的使用

多核处理器技术的普及也帮助降低了单个核的功耗。多个CPU核心可以并行工作,处理不同的任务,允许每个核心在较低的频率和电压下运行,从而降低了整体功耗。

结构与逻辑清晰的深入解析

制程工艺的具体影响

制程工艺的每一步进步都意味着晶体管密度的提升以及功耗的降低。比如,当从14纳米转移到7纳米工艺时,由于晶体管间距的减小,晶体管之间的电容也会降低,这减少了晶体管切换时的能量消耗。制程工艺的这种进步为制造低功耗处理器提供了物理基础。

微架构设计对功耗的影响

微架构设计的改进让CPU在执行同样的任务时可以更高效,这通过减少不必要的计算和提高指令级并行度来实现。现代处理器采用乱序执行和推测执行技术,可以减少因等待数据或指令而产生的空闲周期,从而节省能量。

DVFS技术的应用原理

DVFS技术通过监控CPU的工作负载来动态调整核心电压和频率,从而实现功耗的优化。这项技术依赖于精确的负载预测和快速的电压频率调整机制。当检测到CPU负载下降时,DVFS会及时降低频率和电压,而当负载增加时,它又能迅速提升到合适水平。

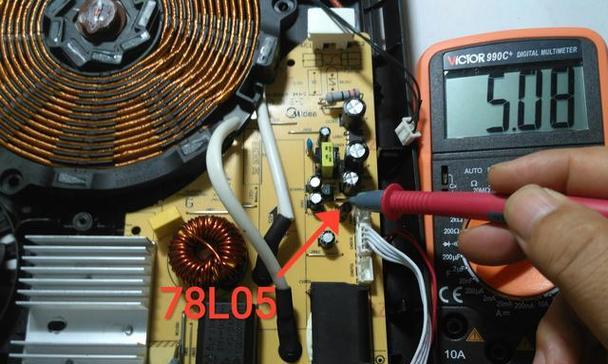

电源门控技术的实现方式

电源门控技术通过在电源和晶体管之间加入开关来实现,当晶体管处于关闭状态时,这些开关会切断电源,避免无谓的功耗。这种技术在现代移动设备中的应用尤为普遍,它能显著降低CPU在待机状态下的功耗。

多核处理器对功耗的优化作用

多核处理器在某些应用中可以更高效地分配任务,因为每个核心可以专注于处理一部分任务,而无需让所有核心都运行在高频率状态。这种并行处理的策略让整体功耗得到控制,而且还能提供更好的多任务处理能力。

用户体验导向的实用建议

了解了CPU功耗降低的原因后,我们可以得出一些实用的建议,这些建议对于消费者和开发者都具有一定的指导意义。

对于消费者来说,了解这些技术背后的原因可以帮助他们作出更明智的硬件选择。在购买笔记本电脑或智能手机时,可以考虑那些使用了先进制程工艺和低功耗设计的产品,以获得更长的电池续航时间。

对于开发者而言,通过编写效率更高、更加优化的代码,可以充分利用现代CPU的节能特性。合理地分配任务到不同的CPU核心,避免不必要的计算,以及优化程序的并行性,都是降低软件运行功耗的有效方法。

结语

CPU功耗降至3w或更低,是多方面技术进步的结果。从更先进的制程工艺到更优化的微架构设计,从动态电压频率调节到电源门控技术的应用,再到多核处理器的普及,这些因素共同作用,使得处理器的功耗得以显著降低。随着科技的不断进步,我们有理由相信未来的处理器将会更加高效、更加节能。